大学共同利用機関法人 高エネルギー加速器研究機構

国立研究開発法人 科学技術振興機構(JST)

本研究成果のストーリー

Question

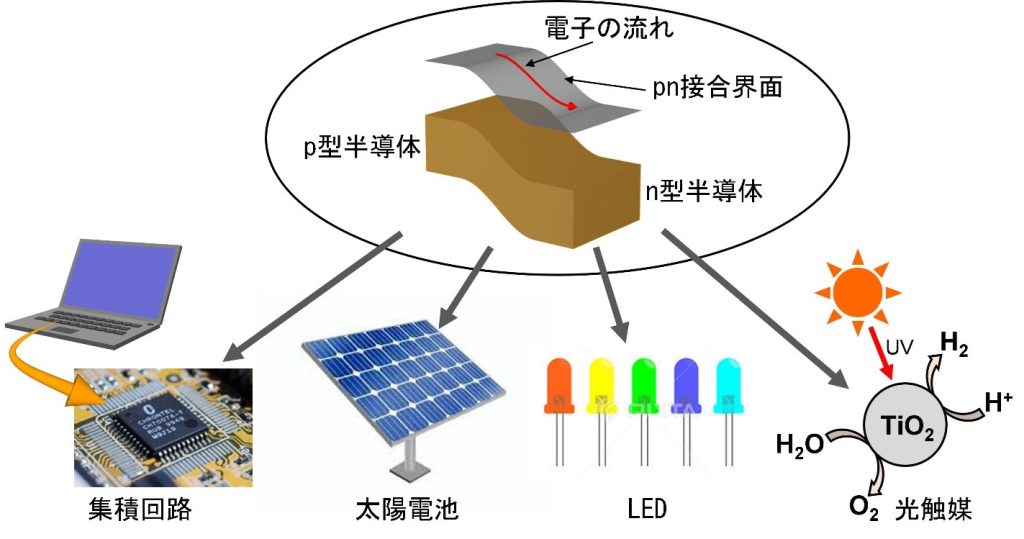

半導体デバイスの中心的な役割を担うp型とn型半導体を接合したpn接合界面が発見されて以来約70年間、pn接合界面が直接観察されることはなかった。

Findings

福本氏が開発した半導体中の伝導電子が可視化できる装置を発展させることで、pn接合界面に形成される電子が空乏化した領域の実空間およびエネルギー空間観測に成功した。

Meaning

この手法は、画像を用いた半導体デバイスの評価を可能にし、あらゆる半導体デバイスに適用できることから、半導体産業の発展に貢献することが期待される。

概要

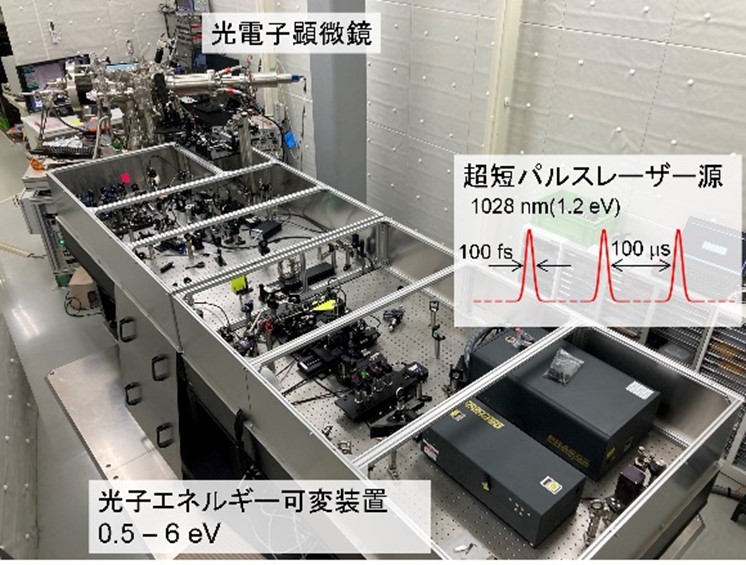

高エネルギー加速器研究機構 物質構造科学研究所に設置されているフェムト秒パルスレーザーを光源とする光電子顕微鏡装置(フェムト秒光電子顕微鏡)(※1)を用いて、半導体デバイスの動作下において、pn接合界面に形成され、電流の制御に重要な役割を担う空乏層(※2)の形状のイメージングに成功しました。この手法は、半導体デバイスの性能を評価しながら、その内部の様子が可視化できる新たな手法として、ダイオード、トランジスタ、太陽電池、LEDなど様々な半導体デバイスへの利用が期待されます。

※1.フェムト秒光電子顕微鏡

励起光を試料に照射して、放出する光電子を投影する顕微鏡(図2)。超短パルスレーザーを光源とすることで、光子エネルギーが近赤外、可視、紫外光の領域で自在に可変となる。これにより、効率良く伝導電子の観測が可能となる。

100fsというとても短い時間だけ、パルスレーザーを照射した。照射と照射の間は100μs(マイクロ(100万分の1)秒)空けた。

※2.空乏層

p型半導体とn型半導体を接合すると、正孔が多いp型半導体の価電子帯と電子が多いn型半導体の伝導帯のエネルギーレベルが揃うように、エネルギーレベルが傾斜をもつ。これにより、電荷キャリアである電子と正孔が存在しない領域(空乏層)が形成される。通常のダイオードでは、順方向に外部電圧を印加すると、傾斜が小さくなり、電荷が流れる。逆方向では、傾斜が大きくなり、電流が流れない。トンネルダイオードでは、空乏層をトンネルするように逆方向バイアスの印加でp型半導体の価電子帯からn型半導体の伝導帯に電子移動する。

詳しくは プレスリリース をご参照ください。

お問い合わせ先

高エネルギー加速器研究機構(KEK)広報室

Tel : 029-879-6047

e-mail : press@kek.jp